I2C vodilo — dodelitev, naprava, prenos podatkov, naslavljanje

Pri ustvarjanju elektronskega vezja se številni razvijalci soočajo s potrebo po uporabi velikega števila vmesnih čipov za ujemanje, vzorčenje in naslavljanje njegovih posameznih blokov. Da bi čim bolj zmanjšal število pomožnih čipov, je Philips že v osemdesetih letih prejšnjega stoletja predlagal dvožilni dvosmerni serijski omrežni vmesnik I2C, zasnovan posebej za upravljanje več čipov znotraj ene naprave.

Samo Philips danes proizvaja več kot sto I2C-združljivih naprav za elektronsko opremo za najrazličnejše namene: pomnilnik, sistemi video procesorjev, analogno-digitalni in digitalno-analogni pretvorniki, gonilniki za zaslone itd.

Vodilo I2C je modifikacija serijskega protokola za izmenjavo podatkov, ki lahko prenaša serijske 8-bitne podatke v običajnem "hitrem" načinu s hitrostjo od 100 do 400 kbps. Proces izmenjave podatkov je tukaj izveden na samo dveh žicah (če ne štejemo skupne žice): SDA liniji za podatke in SCL liniji za sinhronizacijo.

Vodilo postane dvosmerno zaradi dejstva, da imajo kaskade izhodov naprav, povezanih z vodilom, odprte zbiralnike ali kanale, kar posnema ožičenje IN. Kot rezultat, vodilo zmanjša število povezav med čipi, na plošči pa ostane manj potrebnih zatičev in sledi. Posledično se sama plošča izkaže za preprostejšo, kompaktnejšo in tehnološko naprednejšo v izdelavi.

Ta protokol vam omogoča, da onemogočite dekodirnike naslovov in drugo zunanjo pogajalsko logiko. Število čipov, ki lahko delujejo hkrati na vodilu I2C, je omejeno z njegovo zmogljivostjo - največ 400 pF.

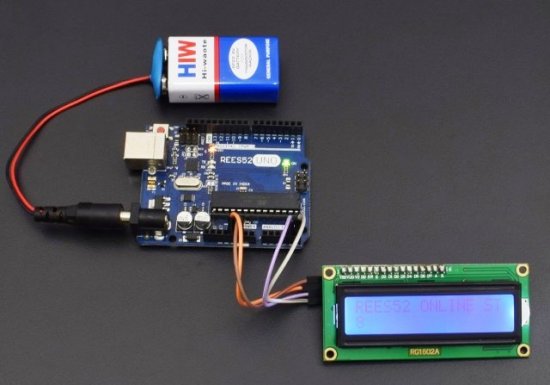

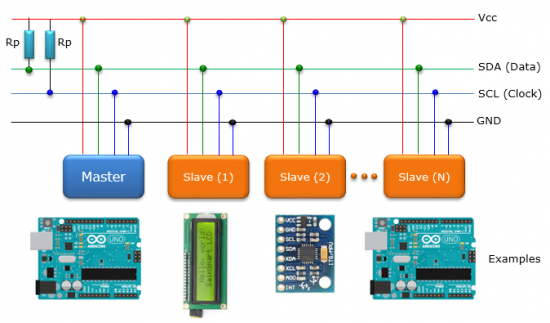

IC-ji, združljivi z I2C, imajo algoritem za dušenje šuma strojne opreme, ki zagotavlja celovitost podatkov tudi v prisotnosti močnih motenj. Takšne naprave imajo vmesnik, ki mikrovezjem omogoča medsebojno komunikacijo, tudi če sta njihovi napajalni napetosti različni. Na spodnji sliki se lahko seznanite z načelom povezovanja več mikrovezij prek skupnega vodila.

Vsaka od naprav, ki so priključene na vodilo, ima svoj edinstveni naslov, ga določa in glede na namen naprave lahko deluje kot sprejemnik ali kot oddajnik. Pri prenosu podatkov so te naprave lahko glavne (master) ali podrejene (slave). Master je naprava, ki sproži prenos podatkov in generira signale ure na liniji SCL. Podrejena naprava je v odnosu do glavne naprave ciljna naprava.

V danem trenutku delovanja na vodilu I2C lahko samo ena naprava deluje kot glavna; generira signal na liniji SCL.Glavni je lahko glavni sprejemnik ali glavni oddajnik.

Načeloma vodilo omogoča več različnih masterjev, vendar nalaga omejitve glede lastnosti oblikovanja krmilnih signalov in spremljanja statusa vodila; to pomeni, da lahko več masterjev začne oddajati hkrati, vendar se tovrstni konflikti odpravijo zaradi arbitraže, torej načina obnašanja masterja, ko zazna, da je vodilo zasedeno z drugim masterjem.

Sinhronizacija para naprav je zagotovljena z dejstvom, da so vse naprave povezane z vodilom in tvorijo ožičenje "IN". Na začetku sta signala SDA in SCL visoka.

START in STOP

Izmenjava se začne z nadrejenim, ki ustvari stanje «START»: na liniji SDA gre signal iz visokega v nizko stanje, medtem ko ima linija SCL stabilno visoko raven. Vse naprave, povezane z vodilom, to situacijo zaznajo kot ukaz za začetek izmenjave.

Vsak master generira individualni taktni signal na liniji SCL pri prenosu podatkov na vodilu.

Izmenjava se konča s tvorjenjem stanja STOP s strani masterja: na liniji SDA se signal spremeni iz nizkega v visok, medtem ko ima linija SCL stabilno visok nivo.

Voznik vedno deluje kot vir signalov START in STOP. Takoj, ko je signal «START» fiksen, to pomeni, da je linija zasedena. Linija je prosta, ko je zaznan signal STOP.

Takoj po razglasitvi stanja START glavni preklopi linijo SCL na nizek nivo in pošlje najpomembnejši bit prvega sporočilnega bajta v linijo SDA. Število bajtov v sporočilu ni omejeno.Spremembe na liniji SDA so omogočene le, ko je nivo signala na liniji SCL nizek. Podatki so veljavni in se jih ne sme spreminjati le, če je sinhronizacijski impulz visok.

Potrditev, da je pomožni sprejemnik sprejel bajt glavnega oddajnika, se izvede z nastavitvijo posebnega potrditvenega bita na liniji SDA po prejemu osmega podatkovnega bita.

POTRDITEV

Torej se pošiljanje 8 bitov podatkov iz oddajnika v sprejemnik konča z dodatnim impulzom na liniji SCL, ko sprejemna naprava pade nizko na linijo SDA, kar kaže, da je prejela celoten bajt.

Potrditev je sestavni del procesa prenosa podatkov. Master ustvari sinhronizacijski impulz. Oddajnik pošlje SDA nizko stanje, medtem ko je potrjena ura aktivna. Medtem ko je sinhronizacijski impulz visok, mora sprejemnik vzdrževati nizek SDA.

Če ciljna podrejena enota ne potrdi svojega naslova, ker je na primer trenutno zasedena, mora biti podatkovna vrstica visoko. Poveljnik lahko nato da signal STOP za prekinitev pošiljanja.

Če sprejem izvaja glavni sprejemnik, potem je dolžan obvestiti pomožni oddajnik po končanem prenosu - ne s potrditvijo zadnjega bajta. Podrejeni oddajnik sprosti podatkovno linijo, tako da lahko glavni odda signal STOP ali ponavljajoči se signal START.

Sinhronizacija naprav je zagotovljena s tem, da so povezave na SCL linijo izvedene po principu "IN".

Poveljnik nima edine pravice nadzorovati prehod linije SCL iz nizke v visoko.Če pomožna enota potrebuje več časa za obdelavo prejetega bita, lahko neodvisno zadrži SCL nizko, dokler ni pripravljena na sprejem naslednjega bita podatkov. Linija SCL bo v takšni situaciji nizka za čas trajanja najdaljšega sinhronizacijskega impulza nizke ravni.

Naprave z najnižjo trajno nizko vrednostjo bodo ostale nedejavne do konca dolgega obdobja. Ko vse naprave končajo obdobje nizke sinhronizacije, bo SCL visok.

Vse naprave bodo začele meriti visoko in prva naprava, ki bo zaključila to obdobje, bo prva nastavila nizko linijo SCL. Posledično bo trajanje nizkega stanja SCL določeno z najdaljšim nizkim stanjem sinhronizacijskega impulza ene od naprav, trajanje visokega stanja pa z najkrajšim obdobjem sinhronizacije ene od naprav. naprave.

Sinhronizacijske signale lahko sprejemniki uporabljajo kot sredstvo za nadzor prenosa podatkov na ravni bitov in bajtov.

Če je naprava sposobna prejemati bajte z visoko hitrostjo, vendar potrebuje določen čas, da shrani prejeti bajt ali se pripravi na sprejem naslednjega bajta, lahko po prejemu in potrditvi bajta še naprej ohranja nizek SCL, kar prisili oddajnik v stanje pripravljenosti.

Mikrokrmilnik brez vgrajenih vezij strojne opreme, na primer na bitni ravni, lahko upočasni takt s podaljšanjem trajanja nizkega stanja. Posledično bo hitrost prenosa glavne naprave določena s hitrostjo počasnejša naprava.

NASLOVALJANJE

Vsaka naprava, ki je priključena na vodilo I2C, ima edinstven programski naslov, na katerega jo glavni naslovi s pošiljanjem določenega ukaza. Za mikrovezja iste vrste je značilen izbirnik naslovov, ki je izveden bodisi v obliki digitalnih vhodov izbirnika bodisi v analogni obliki. Naslovi so razdeljeni v naslovni prostor naprav, povezanih z vodilom.

Normalni način predvideva sedembitno naslavljanje. Naslavljanje deluje na naslednji način: po ukazu «START» master pošlje prvi bajt, ki določa, katera podrejena naprava je potrebna za komunikacijo z masterjem. Obstaja tudi skupni klicni naslov, ki definira vse naprave na vodilu, vse naprave (teoretično) nanj odgovorijo s potrditvijo, v praksi pa je to redko.

Prvih sedem bitov prvega bajta je torej podrejeni naslov. Najmanj pomemben bit, osmi, označuje smer pošiljanja podatkov. Če je »0«, bodo informacije zapisane od nadrejene v to podrejeno. Če je «1», bo glavni prebral informacije iz tega podrejenega.

Ko glavni konča s pošiljanjem naslovnega bajta, vsak podrejeni primerja svoj naslov z njim. Vsakdo z enakim naslovom je podrejeni in je definiran kot podrejeni oddajnik ali podrejeni sprejemnik, odvisno od vrednosti najmanj pomembnega bita naslovnega bajta.

Podrejeni naslov lahko vključuje fiksne in programabilne dele. Pogosto v enem sistemu deluje veliko število naprav istega tipa, potem programabilni del naslova omogoča uporabo največ istega tipa naprav na vodilu. Koliko bitov v naslovnem bajtu je mogoče programirati, je odvisno od števila prostih pinov na čipu.

Včasih zadošča pin z analogno nastavitvijo programabilnega obsega naslovov, na primer SAA1064 - gonilnik LED indikatorja, ki ima točno takšno izvedbo. Potencial določenega pina določa odmik naslovnega prostora čipa, tako da čipi istega tipa ne nasprotujejo delujočim na istem vodilu. Vsi čipi, ki podpirajo vodilo I2C, vsebujejo nabor naslovov, ki jih proizvajalec navede v dokumentaciji.

Kombinacija «11110XX» je rezervirana za 10-bitno naslavljanje. Če si predstavljamo izmenjavo podatkov od ukaza «START» do ukaza «STOP», bo to izgledalo takole:

Tu so dovoljeni enostavni in kombinirani formati izmenjave podatkov. Kombinirani format pomeni, da lahko med «START» in «STOP» glavni in podrejeni delujeta kot sprejemniki in oddajniki, kar je uporabno na primer pri upravljanju serijskega pomnilnika.

Naj prvi bajt podatkov prenese pomnilniški naslov. Nato s ponavljanjem ukaza «START» in branjem podrejenega naslova bodo pomnilniški podatki delovali. Odločitve o samodejnem povečanju ali zmanjšanju prej dostopanega naslova sprejme razvijalec naprave po predhodnem preučevanju dokumentacije čipa. Tako ali drugače morajo vse naprave po prejemu ukaza START obnoviti svojo logiko in se pripraviti na dejstvo, da bo naslov zdaj poimenovan.