Digitalne naprave: flip-flopi, komparatorji in registri

Digitalne naprave so zgrajene na logičnih elementih, zato upoštevajo zakone logične algebre. Osnovne naprave digitalne tehnike so poleg logičnih naprav natikači.

Digitalne naprave so zgrajene na logičnih elementih, zato upoštevajo zakone logične algebre. Osnovne naprave digitalne tehnike so poleg logičnih naprav natikači.

Sprožilec (angleški trigger - sprožilec) - elektronska naprava, ki ima dve stabilni stanji in lahko pod vplivom zunanjega impulza preskoči iz enega stanja v drugega.

Sprožilci ali, natančneje, sprožilni sistemi se imenujejo širok razred elektronskih naprav, ki imajo sposobnost, da dolgo časa ostanejo v enem od dveh stabilnih stanj in ju izmenjujejo pod vplivom zunanjih signalov. Vsako stanje sprožitve je enostavno prepoznati po vrednosti izhodne napetosti.

Vsako stanje sprožitve ustreza določeni (visoki ali nizki) ravni izhodne napetosti:

1) sprožilec je nastavljen na eno stanje — raven «1».

2) flip-flop se ponastavi - raven «0» na izhodu.

Stabilno stanje ostane poljubno dolgo in se lahko spremeni z zunanjim impulzom ali z izklopom napajalne napetosti. Che.flip-flop je elementarni pomnilniški element, ki lahko shrani najmanjšo enoto informacije (en bit) «0» ali «1».

Japonke so lahko zgrajene na diskretnih elementih, logičnih elementih, na integriranem vezju ali pa so del integriranega vezja.

Glavne vrste japonk so: RS-, D-, T-, in JK-fliperji... Poleg tega se japonke delijo na asinhrone in sinhrone. Pri asinhronem aktiviranju se preklop iz enega stanja v drugega izvede neposredno s prihodom signala na informacijski vhod. Poleg podatkovnih vhodov imajo sinhronizirani japonke še taktni vhod. Njihovo preklapljanje poteka le ob prisotnosti omogočitvenega taktnega impulza.

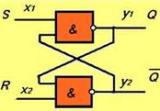

Sprožilec RS ima vsaj dva vhoda: S (set — set) — sprožilec je nastavljen na nivo «1» in R (reset) — sprožilec se ponastavi na nivo «0». (slika 1).

Ob prisotnosti vhoda C je flip-flop sinhron - preklapljanje flip-flopa (sprememba stanja izhoda) se lahko pojavi le v trenutku prihoda sinhronizacijskega (sinhronizacijskega) impulza na vhod C.

Slika 1 - Običajni grafični prikaz flip-flopa RS in namen zaključkov a) asinhroni, b) sinhroni

Poleg neposrednega izhoda ima lahko flip-flop tudi inverzni izhod, katerega signal bo nasproten.

Tabela 1 prikazuje stanja, ki jih lahko prevzame flip-flop med delovanjem. Tabela prikazuje vrednosti vhodnih signalov S in R v določenem trenutku časa tn in stanje flip-flopa (direktnega izhoda) v naslednjem trenutku časa tn + 1 po prihodu naslednjega stročnice. Na novo stanje sprožilca vpliva tudi prejšnje stanje Q n.

Che.če je treba zapisati na sprožilec «1» - damo impulz na vhod S, če je «0» - pošljemo impulz na vhod R.

Kombinacija S = 1, R = 1 je prepovedana kombinacija, ker je nemogoče predvideti, kakšno stanje se bo vzpostavilo na izhodu.

Tabela 1 - Tabela stanj sinhronega RS flip-flopa

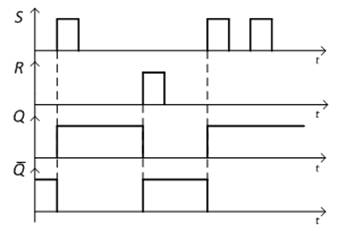

Delovanje flip-flopa lahko vidimo tudi s pomočjo časovnih diagramov (slika 2).

Slika 2 — Časovni diagrami asinhronega flip-flopa RS

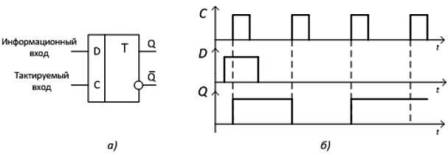

D-trigger (iz angleščine delay - zamuda) ima en informacijski vhod in taktni (sinhronizacijski) vhod (slika 3).

D-flip-flop shrani in shrani na izhodu Q signal, ki je bil na podatkovnem vhodu D v času prihoda taktnega impulza C. flip-flop shrani informacijo, zapisano, ko je C = 1.

Tabela 2-Tabela stanj D-flip-flopa

Slika 3 — D-sprožilec: a) običajna grafična predstavitev, b) časovni diagrami delovanja

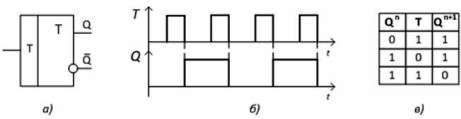

T-sprožilci (iz angleškega tumble - prevračanje, salto), imenovani tudi štetje flip-flopov, imajo en informacijski vhod T. Vsak impulz (razpad impulza) T-vhoda (štetje vhoda) preklopi sprožilec v nasprotno stanje.

Slika 4 prikazuje simbologijo T-sprožilca (a) in časovne diagrame delovanja (b).

Slika 4-T-flip-flop a) konvencionalno-grafični zapis, b) časovni diagrami delovanja c) tabela stanj

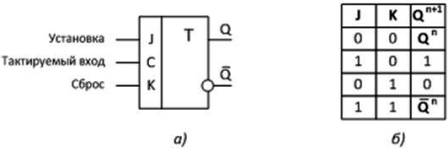

Sprožilec JK (iz angleškega jump — skok, keer — drži) ima dva podatkovna vhoda J in K ter taktni vhod C. Razporeditev pinov J in K je podobna dodelitvi pinov R in S, vendar ima prožilec brez prepovedanih kombinacij. Če je J = K = 1, spremeni svoje stanje v nasprotno (slika 5).

Ob ustrezni povezavi vhodov lahko sprožilec opravlja funkcije RS-, D-, T-prožilcev, t.j. je univerzalni sprožilec.

Slika 5 - JK - flip-flop a) konvencionalni - grafični zapis, b) skrajšana tabela stanj

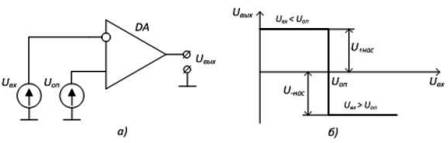

Primerjalnik (primerjaj — primerjaj) — naprava, ki primerja dve napetosti — vhod Uin z referenčnim Uref. Referenčna napetost je konstantna napetost s pozitivno ali negativno polariteto, vhodna napetost se s časom spreminja. Najenostavnejše primerjalno vezje na osnovi operacijskega ojačevalnika je prikazano na sliki 6, a. Če je Uin Uop na izhodu U — us (slika 6, b).

Slika 6 — Op-amp primerjalnik: a) najpreprostejša shema b) karakteristike delovanja

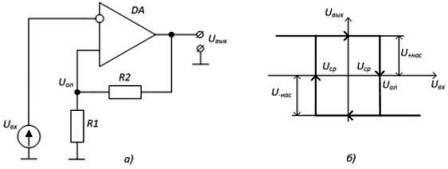

Primerjalnik s pozitivno povratno zvezo se imenuje Schmittov prožilec. Če primerjalnik preklopi iz «1» v «0» in obratno pri isti napetosti, potem Schmittov sprožilec - pri različnih napetostih. Referenčna napetost ustvari PIC vezje R1R2, vhodni signal se napaja na invertni vhod operacijskega ojačevalnika. Slika 7, b, prikazuje karakteristiko prenosa Schmittovega sprožilca.

Pri negativni napetosti na inventarnem vhodu OS Uout = U + sat. To pomeni, da na neinvertirajočem vhodu deluje pozitivna napetost. Ko se vhodna napetost poveča, je tok Uin > Uneinv. (Uav — sprožilec) primerjalnik preide v stanje Uout = U -sat. Na neinvertirajoči vhod se uporabi negativna napetost. V skladu s tem z zmanjšanjem vhodne napetosti v trenutku Uin <Uneinv. (Uav — sprožilec) primerjalnik preide v stanje Uout = U + sat.

Slika 7 — Schmittovo delovanje operacijskega ojačevalnika: a) najpreprostejša shema b) karakteristike delovanja

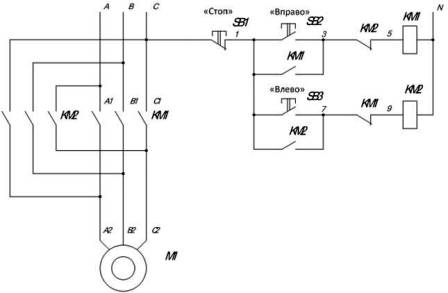

Primer. Slika 8 prikazuje shemo releja-kontaktorja za krmiljenje elektromotorja, ki mu omogoča zagon, zaustavitev in vzvratno vožnjo.

Slika 8 — Krmilna shema motorja z relejnim kontaktorjem

Komutacijo elektromotorja izvajajo magnetni zaganjalniki KM1, KM2. Prosto zaprti kontakti KM1, KM2 preprečujejo sočasno delovanje magnetnih zaganjalnikov. Prosto odprti kontakti KM1, KM2 zagotavljajo samozaklepanje tipk SB2 in SB3.

Za izboljšanje zanesljivosti delovanja je treba zamenjati krmilna vezja rele-kontaktorja in močnostna vezja z brezkontaktnim sistemom z uporabo polprevodniških naprav in naprav.

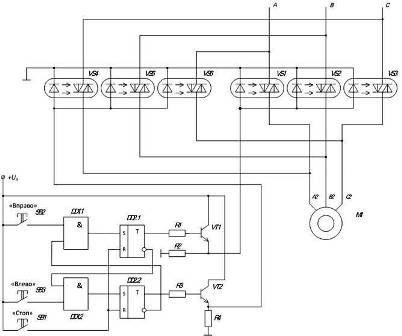

Slika 9 prikazuje brezkontaktno krmilno vezje motorja.

Močnostni kontakti magnetnih zaganjalnikov so bili zamenjani z opto-simistorji: KM1-VS1-VS3, KM2-VS4-VS6. Uporaba optosimistorjev omogoča izolacijo krmilnega vezja nizkega toka od močnega napajalnega vezja.

Sprožilci zagotavljajo samozaklepne gumbe SB2, SB3. Logični elementi IN zagotavljajo hkratno aktiviranje samo enega od magnetnih zaganjalnikov.

Ko se tranzistor VT1 odpre, tok teče skozi LED prve skupine opto-simistorjev VS1-VS3 in s tem zagotovi pretok toka skozi navitja motorja.Odprtina tranzistorja VT2 napaja drugo skupino opto-simistorjev VS4 -VS6, ki zagotavlja vrtenje elektromotorja v drugo smer.

Slika 9 — Brezkontaktno krmilno vezje motorja

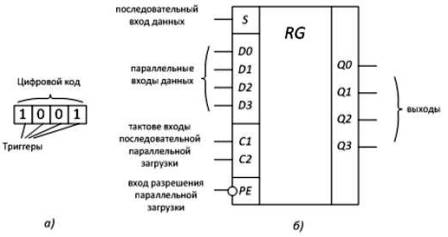

Register - elektronska naprava, namenjena kratkotrajnemu shranjevanju in pretvorbi večmestnih binarnih števil. Register je sestavljen iz flip-flopov, katerih število določa, koliko bitov binarnega števila lahko shrani register - velikost registra (slika 10, a). Logične elemente je mogoče uporabiti za organizacijo delovanja sprožilcev.

Slika 10 — Register: a) splošni prikaz, b) konvencionalni grafični zapis

Glede na način vnosa in izhoda informacij delimo registre na vzporedne in serijske.

V sekvenčnem registru sta flip-flopa povezana zaporedno, to pomeni, da izhodi prejšnjega flip-flopa podajajo informacije na vhode naslednjega flip-flopa. Urni vhodi flip-flopa C so povezani vzporedno. Tak register ima en podatkovni vhod in krmilni vhod - urni vhod C.

Vzporedni register istočasno piše na flip-flope, za katere obstajajo štirje podatkovni vhodi.

Slika 10 prikazuje UGO in razporeditev pinov štiribitnega paralelno-serijskega registra.